关键词:XADC,PYNQ Z2, XADC IP核, PL

说明 : 不涉及xadc开发板,PCB设计,可以跳过前面看后面,不正确的地方可以交流沟通,待完善

一. 对于xadc基本了解

1. 基本属性

参考手册 : ug480

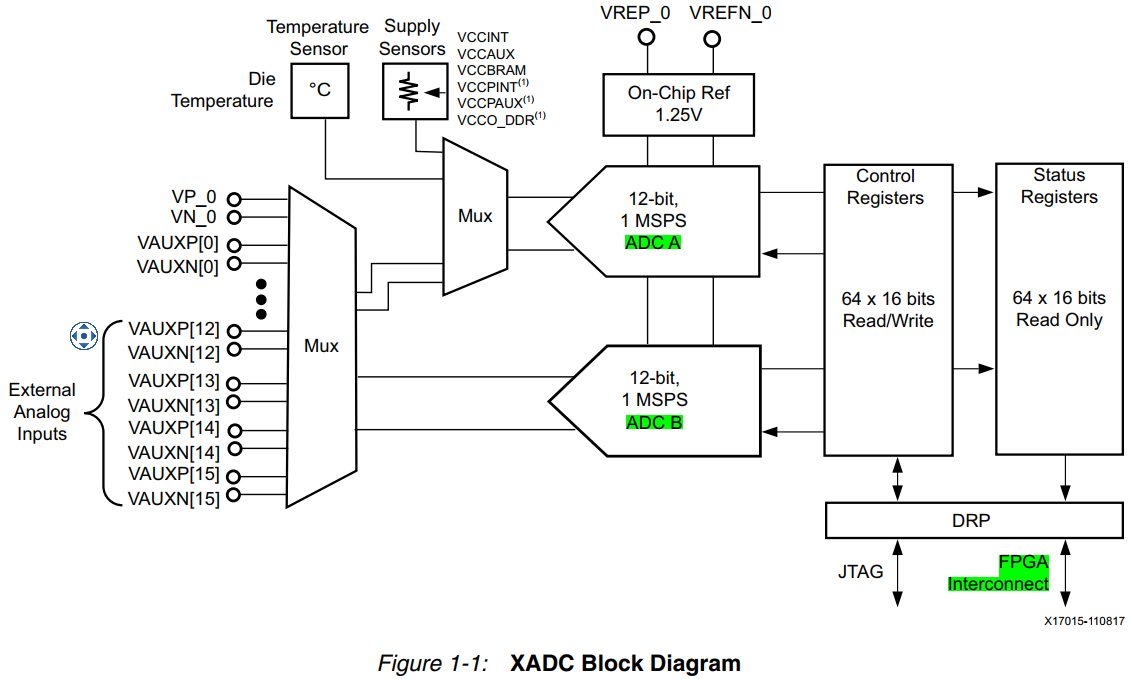

Fig : XADC BLOCK DIAGRAM:

从XADC block diagram中可以看出7系含有两个内部ad, ADCA,ADCB

同时可以支持16组外部差分通道,但是VP_0,VN_0为特殊的差分通道,其余的则是可以支持单端或者差分模式

两个ADC均为12bit,1MSPS, 实际数据有16bit, 由于LSB 4 bit由于精度太高,导致波动较大,因此可以取MSB12 bit作为需要的数据

ADCA不仅可以采集外部通道, 同时也可以采集板载内部通道如温度,各种内部电压,temperature sensor and supply sensor

ADCB只可以采集外部通道,同时在使用过程中可以只使用ADCA,而不使用ADCB,可以将其配置为掉电模式,从而节省功耗开销

在使用xadc外部通道的时候只需要将对应的差分引脚引出,设置为input, io std设置为bank电压,通常为LVCOM33

手册上已经说明了VREF为1.25V,实际的话….可以测一测

![图片[1]-7系XADC在PL端使用-编程算法牛翰社区-数据算法-牛翰网](https://niuimg.niucores.com/wp-content/uploads/2024/10/7097216941397738948.png)

虽然外部通道为在xadc被设置为差分通道,但是可以使用为单端通道,具体可以根据自己开发板查看, 在ug480中对此有说明

Fig2: 差分与单端

2. XADC数据读取方式

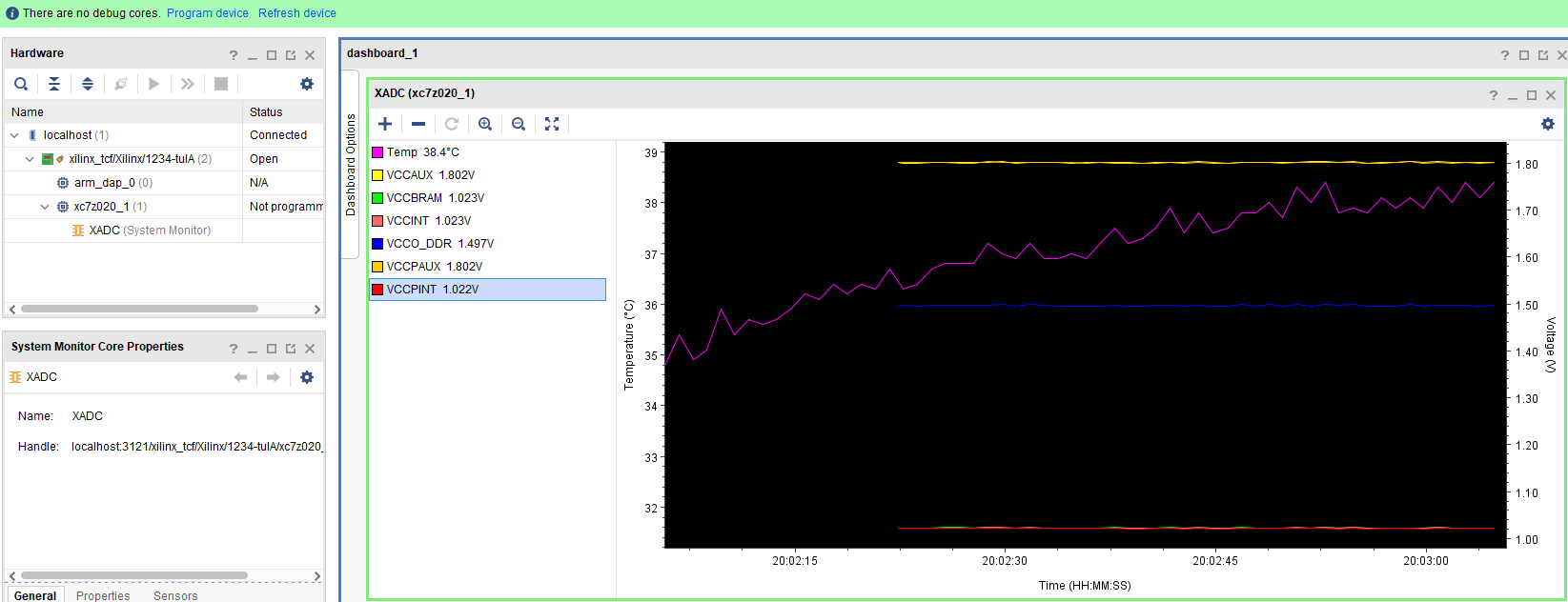

在使用xadc的时候可以使用DRP / JTAG模式, DRP需要我们进行编写,可以使用xadc ip核,另外可以使用JATG直接读取

DRP在下面展开,此处简短说明JTAG,当使用xilinx开发工具连接7系开发板会出现XADC,我们打开后点击+,可以直接读取且尽可读取temperature sensor以及supply sensor的值,无法读取外部通道数据,这被称为缺省模式

Fig : JATG读取数据示例

3. 采样时序

XADC采样模式有连续采样, 事件采样

连续采样就一直采集,配置的通道数循环采集

事件采样则是自己给采样的触发信号

4. XADC端口

Fig : XADC 端口

![图片[2]-7系XADC在PL端使用-编程算法牛翰社区-数据算法-牛翰网](https://niuimg.niucores.com/wp-content/uploads/2024/10/2279688597964774495.png)

Fig : XADC寄存器

![图片[3]-7系XADC在PL端使用-编程算法牛翰社区-数据算法-牛翰网](https://niuimg.niucores.com/wp-content/uploads/2024/10/135918097097854586.png)

Fig: 外部通道地址

![图片[4]-7系XADC在PL端使用-编程算法牛翰社区-数据算法-牛翰网](https://niuimg.niucores.com/wp-content/uploads/2024/10/8479126083462307277.png)

细节在手册46页

XADC内部的寄存器有众多,可以通过DRP接口进行读写,部分寄存器为只读模式

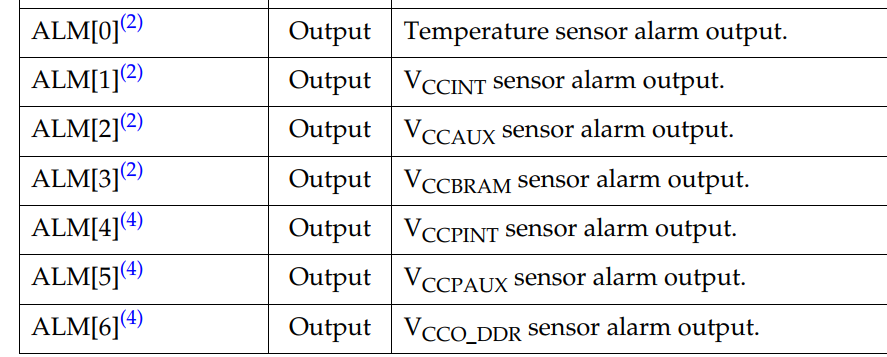

端口说明

DRP_DO : XADC的输出, 为采集到的值

DRP_DI : XADC的输入, 对于可写寄存器写入的值

DRP_DADDR : XADC的输入, 指向寄存器的地址,当我们只需要采集不需要配置的时候, 比如获取只读寄存器的值,我们只需要向DADDR传入寄存器地址, DRP_IO则不需要处理, 对于需要配置寄存情况,在传输地址的同时传输数据

DRP_DEN : DRP整个接口的开始信号

DRP_DWE : DRP接口写入使能

DRP_DCLK : 时钟信号

DRP_DRDY : XADC有好几个内部完成信号,可以查看手册进行区别,这里这个信号我在使用的时候,此信号被拉高,就可以直接读取数据了

control and clock :

包含复位信号,

CONVST用于采样模式为事件采样的开始信号

External Analogy inputs : 外部通道需要我们在模块里面设计成输入信号,连接外部引脚

Alarms : 使用IP核或者直接向寄存器进行配置,设置不同的报警信号,主要是针对于temperature sensor and supply sensor这几个信号进行阈值设计,超出阈值后,会将信号拉高,从而达到报警目的

Alarms是一个8bit的数据,每个bit所代表的报警通道不一样

Status : XADC的输出信号, 我们可以用来作为标志位,我挑选两个重要的描述

EOC : end of conversion,单个通道数据转换完成信号,转换完成拉高,表示采集ok了

End of conversion signal. This signal transitions to active-High at the end of an ADC conversion when the measurement is written to the status registers

EOS : 当我们多个通道连续采样模式的时候,轮巡完一遍的末尾会将次信号拉高

End of sequence. This signal transitions to active-High when the measurement data from the last channel in an automatic channel sequence is written to the status registers.

BUSY : 在很多protocol里面会出现,此信号表示器件处于非空闲状态,我们的读写最好不要在器件忙碌期间进行操作

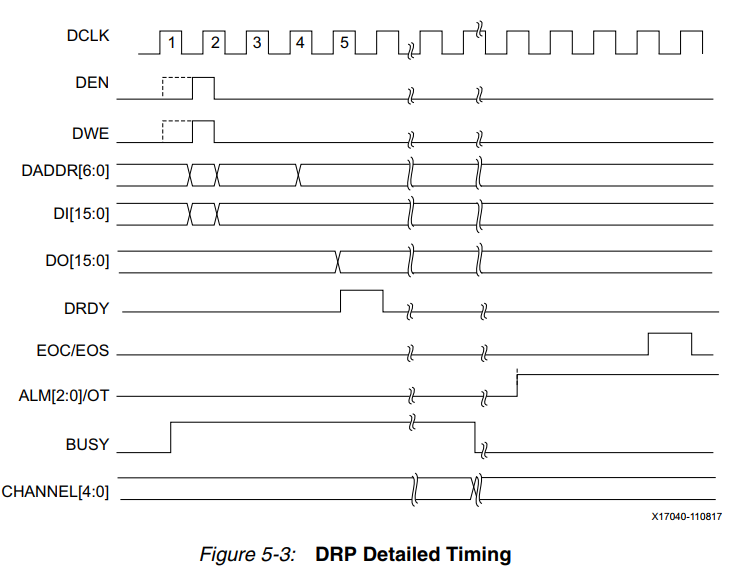

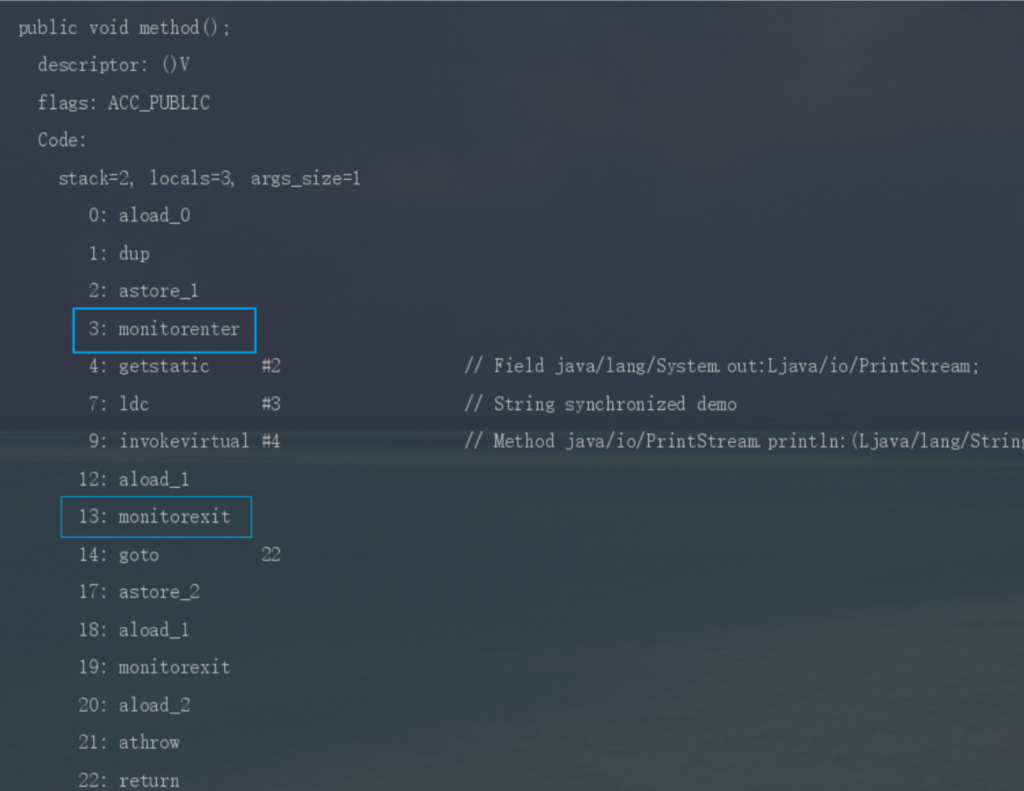

4.操作时序

Fig : DRP Timing

我对这部分理解不是很深我选择连续采样,但是使用DRP timing, 我大概是用错的,但是理论上也没关系,因为都是DRP接口

我使用的是DRP timing,在Busy信号空闲时间输入通道的时候向ADDR传入我要采集的寄存器地址,他给我返回数据

既然他设计了DRP端口,那就应该可以在空闲的时候进行寄存器地址传输,或者自己设计一些列表数据向里面传输,那是不是和多通道一样呢,TODO

有对这部分有理解的大佬可以留言交流探讨

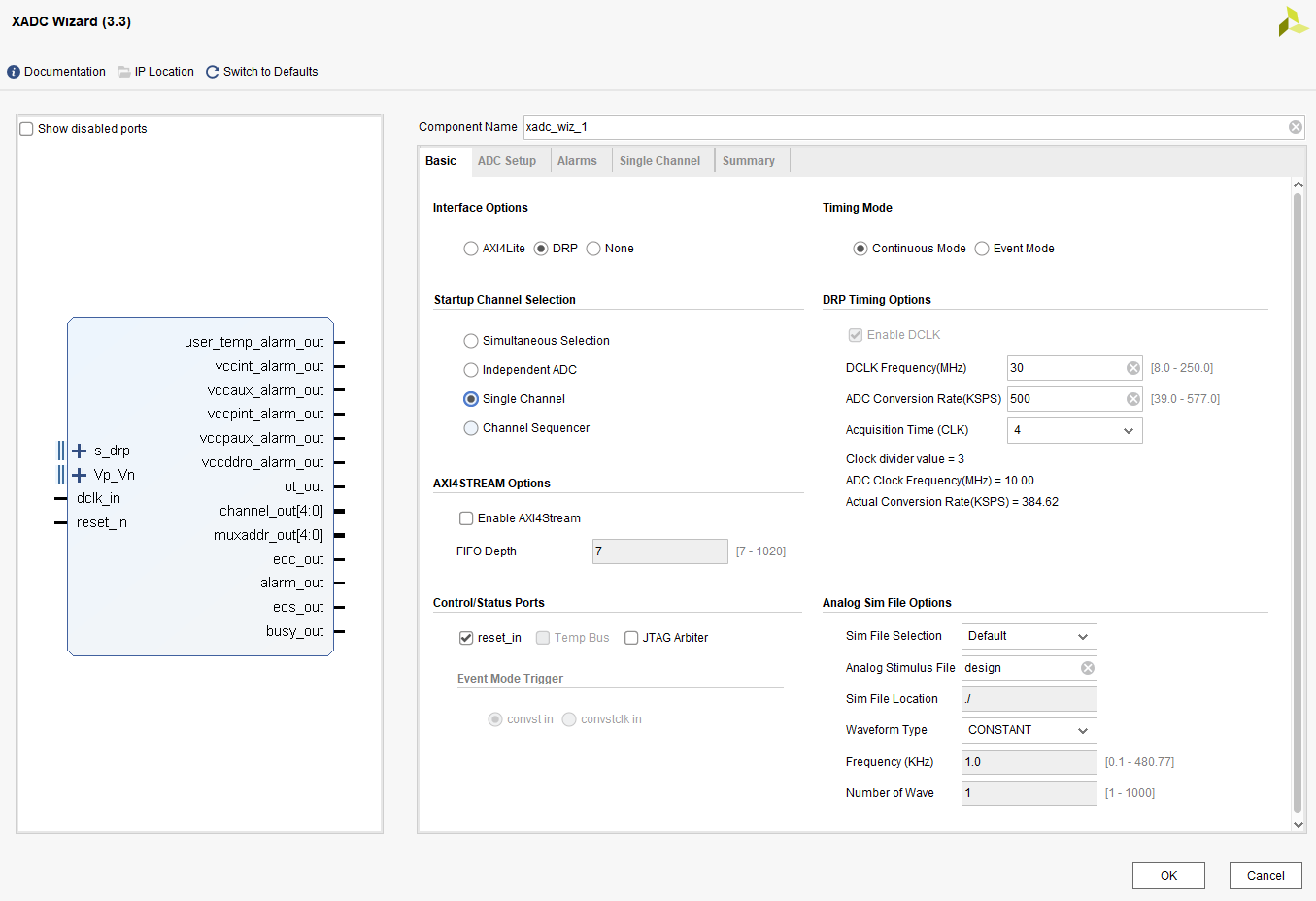

二. 开始使用

使用XADC IP核

Fig : BASIC

接口选择

接口可以选择AXI lite 或者DRP, None没咋看

axi lite接口一般是使用ps读取xadc的时候使用,将数据给ps处理

在PL端处理就选择DRP接口

时序模式

根据需求选择连续模式或者自己设置触发信号

startup channel select

一般选择single channel 或者 channel sequencer

DRP Timing Options

根据自己需要的采样率去进行时钟频率配置

Acquisition time : 需要几个clk能完成数据转换

axi stream

将采集数据使用axi stream给ps用的

control port

可以选择复位选项

analogy sim file option

系统自带的用于仿真的用的,可以不予处理

Fig : ADC_Setup

![图片[5]-7系XADC在PL端使用-编程算法牛翰社区-数据算法-牛翰网](https://niuimg.niucores.com/wp-content/uploads/2024/10/183514219173404565.png)

sequencer mode没看

channel avg : 可以进行选择16,64,256个数据进行取平均,在xadc内部进行,一般我们读取出来以后自己进行滤波

ADC / Supply Sensor Calibration

可以对adc和供电进行矫正

外部通道多路复用选择器

应该是值第一个指向那个通道,我选择了VAUXP1 VAUXN1, 指向外部通道1

同时我将ADCB掉电了,不使用ADCB

Alarm

![图片[6]-7系XADC在PL端使用-编程算法牛翰社区-数据算法-牛翰网](https://niuimg.niucores.com/wp-content/uploads/2024/10/509009171865611299.png)

我没有使用任何报警信号,自己可以配置,设置阈值

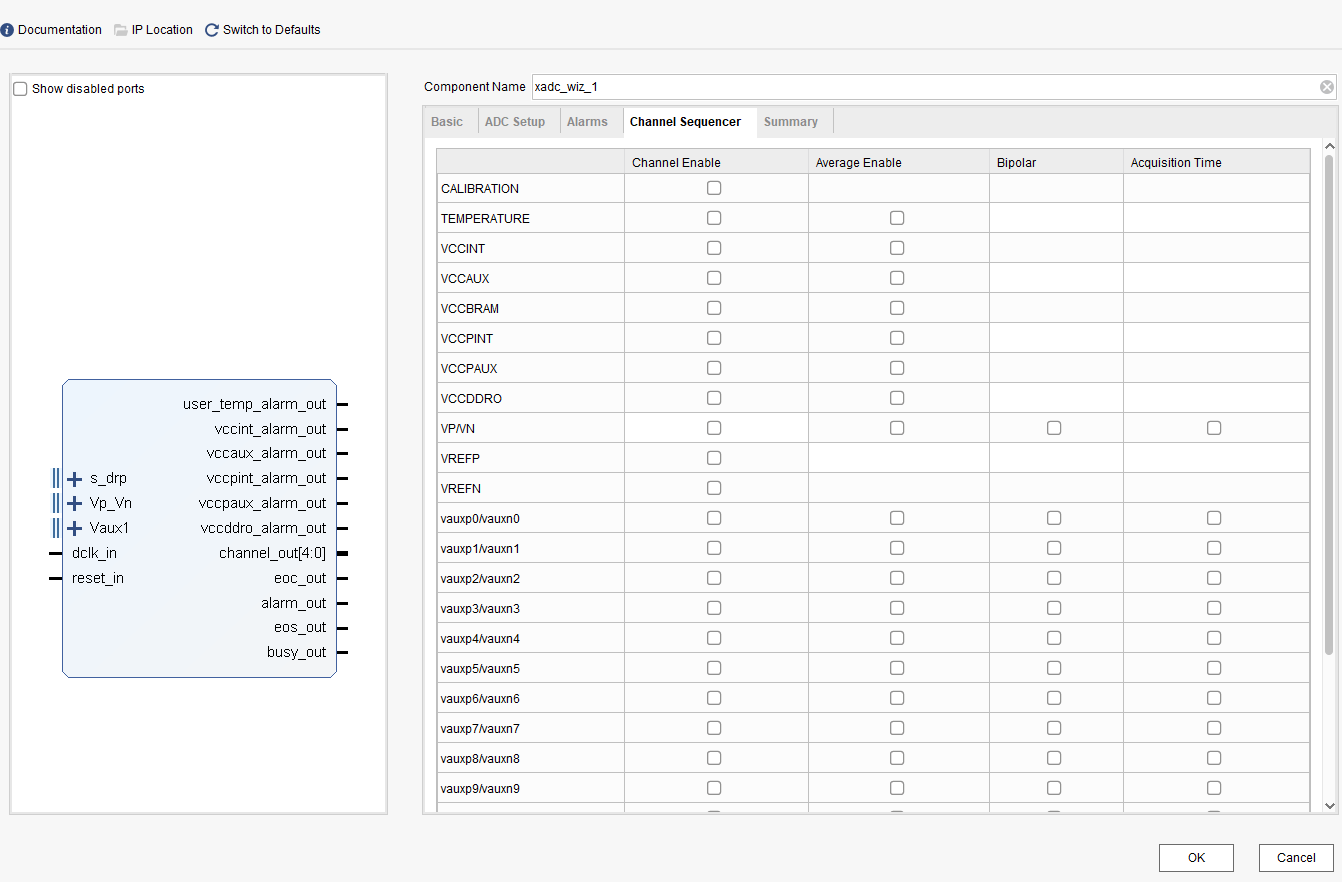

Single channel

![图片[7]-7系XADC在PL端使用-编程算法牛翰社区-数据算法-牛翰网](https://niuimg.niucores.com/wp-content/uploads/2024/10/7005047506551727079.png)

我选择的是单通道采集

如果不是单通道采集,而是多通道的会出现如下图

最后就配置完成了

赋值voe模板如下

xadc_wiz_0 your_instance_name (

.di_in(di_in), // input wire [15 : 0] di_in

.daddr_in(daddr_in), // input wire [6 : 0] daddr_in

.den_in(den_in), // input wire den_in

.dwe_in(dwe_in), // input wire dwe_in

.drdy_out(drdy_out), // output wire drdy_out

.do_out(do_out), // output wire [15 : 0] do_out

.dclk_in(dclk_in), // input wire dclk_in

.reset_in(reset_in), // input wire reset_in

.vp_in(vp_in), // input wire vp_in

.vn_in(vn_in), // input wire vn_in

.vauxp1(vauxp1), // input wire vauxp1

.vauxn1(vauxn1), // input wire vauxn1

.channel_out(channel_out), // output wire [4 : 0] channel_out

.eoc_out(eoc_out), // output wire eoc_out

.alarm_out(alarm_out), // output wire alarm_out

.eos_out(eos_out), // output wire eos_out

.busy_out(busy_out) // output wire busy_out

);

根据自己需求进行信号选取

我设计的是, 同时需要一个pll IP核得到30MHz信号

// port for xadc

xadc_wiz_0 xadc_inst (

.di_in (xadc_din ), // input wire [15 : 0] di_in

.daddr_in (addr ), // input wire [6 : 0] daddr_in

.den_in (xadc_en ), // input wire den_in

.dwe_in (xadc_wen ), // input wire dwe_in

.drdy_out (xadc_drdy ), // output wire drdy_out

.do_out (xadc_dout ), // output wire [15 : 0] do_out

.dclk_in (clk_30mhz ), // input wire dclk_in

.reset_in (rst_p ), // input wire reset_in

.vp_in ( ), // input wire vp_in

.vn_in ( ), // input wire vn_in

.vauxp1 (ch1_p ), // input wire vauxp1

.vauxn1 (ch1_n ), // input wire vauxn1

.channel_out( ), // output wire [4 : 0] channel_out

.eoc_out (xadc_eoc ), // output wire eoc_out

.alarm_out ( ), // output wire alarm_out

.eos_out ( ), // output wire eos_out

.busy_out (xadc_busy ) // output wire busy_out

);

模块输入输出端口信号为

module top(

input wire clk_125mhz ,

input wire rst_p ,

input wire ch1_p ,

input wire ch1_n ,

input wire key ,

output wire led

);

将ch1_p, ch1_n进行管脚约束即可,io std 选择的是LVCOM33, vivado最后会识别出这个管脚是analogy pin.

三. ILA 数据抓取

将通道1接GND

![图片[8]-7系XADC在PL端使用-编程算法牛翰社区-数据算法-牛翰网](https://niuimg.niucores.com/wp-content/uploads/2024/10/2429834186946988005.png)

将通道1接3.3V

![图片[9]-7系XADC在PL端使用-编程算法牛翰社区-数据算法-牛翰网](https://niuimg.niucores.com/wp-content/uploads/2024/10/8763766175344266867.png)

数据是原始数据,未进行任何处理,同时这个值与开发板原理图有关所以GND不为0

code : https://github.com/tiruoQing/fpgas/blob/main/xadc/single_channel

没有回复内容