电源管脚接触测试(Power Pin Contact Test)是芯片量产/测试流程中用于确认芯片电源引脚(如 VDD、VSS、AVDD、DVDD 等)是否与测试治具或探针台良好接触的关键测试环节。

1.为什么要做电源管脚接触测试?

电源管脚如果接触不良,可能导致:

- 芯片无法正常上电,所有后续测试失效

- 功耗异常、读写失败等误判

- 烧坏芯片或探针卡

所以在 功能测试前必须验证电源管脚接触良好。

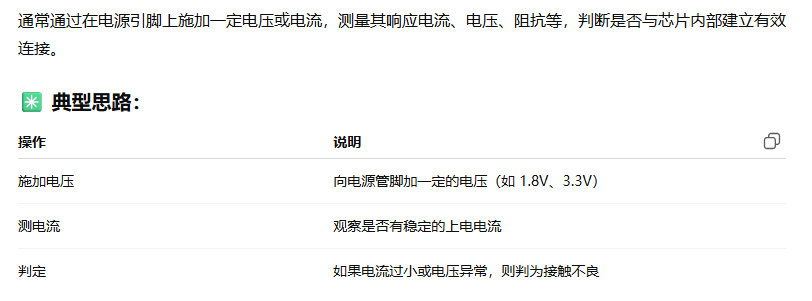

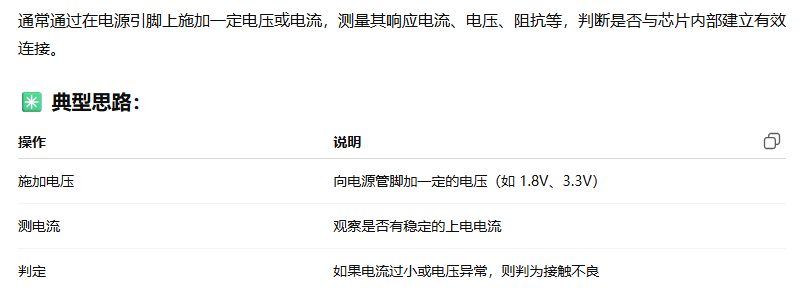

2.电源管脚接触测试的基本原理

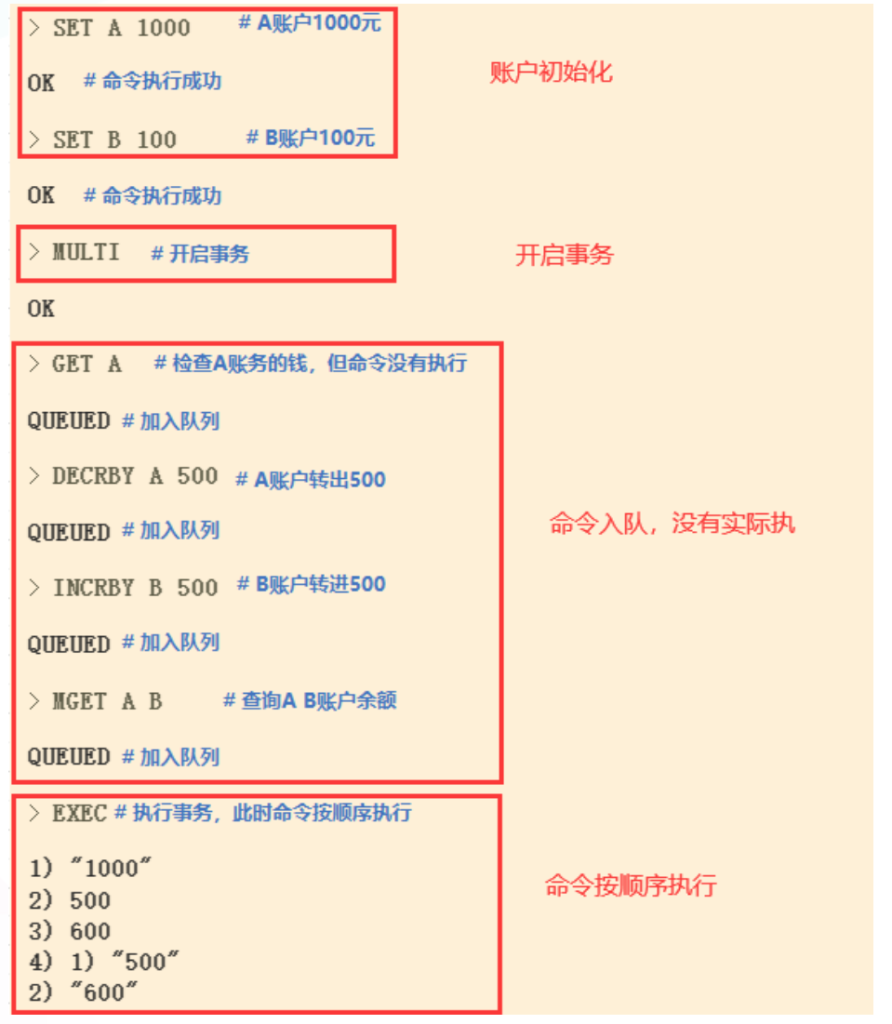

3.常见测试流程(以 PXI 系统 + SMU 为例)

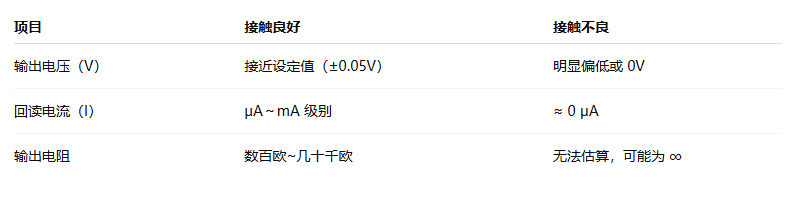

4.电源接触良好/不良典型表现

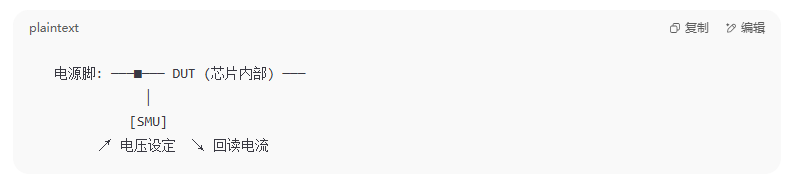

5.接触测试波形示意(简化)

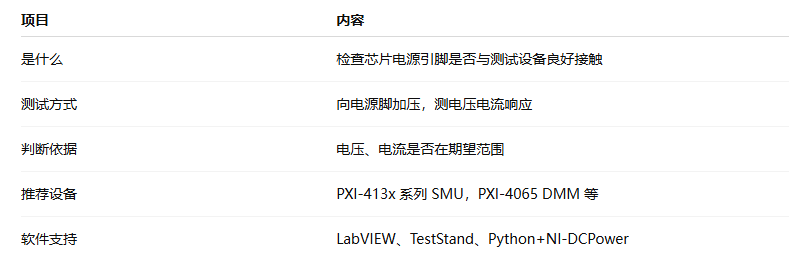

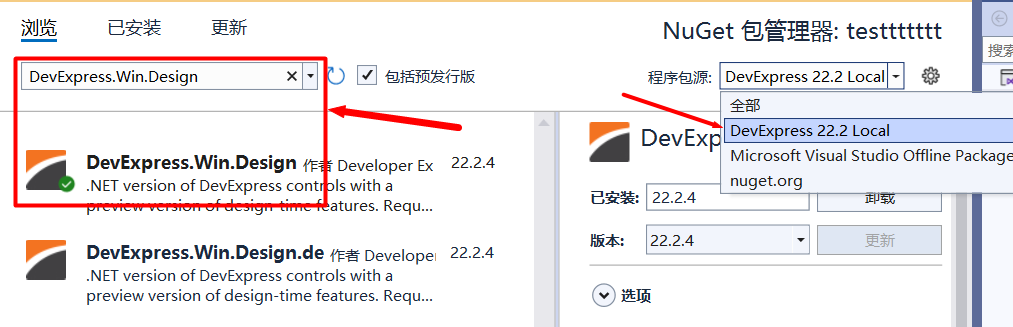

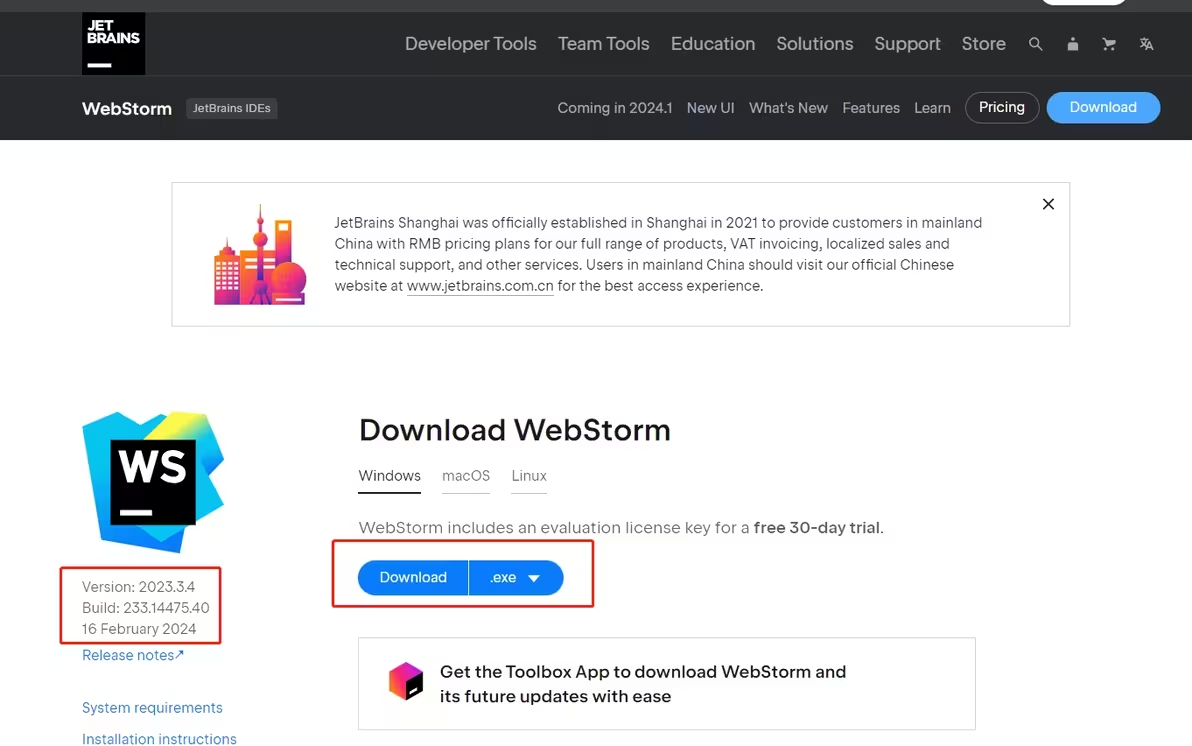

6.适用 NI 设备

7.注意事项

-

电源脚连接应逐一检查,特别是模拟电源、数字电源、参考电源(如 AVDD、DVDD、VREF)

-

设置合理的限流值,避免芯片损坏

-

若有多个电源轨,需独立测试每一个电源引脚

8.总结

以上就是电源管脚测试的简单介绍。

如果本文介绍对你有帮助,可以一键四连:点赞+评论+收藏+推荐,谢谢!

来源链接:https://www.cnblogs.com/chenshibao/p/18946545

© 版权声明

本站所有资源来自于网络,仅供学习与参考,请勿用于商业用途,否则产生的一切后果将由您(转载者)自己承担!

如有侵犯您的版权,请及时联系3500663466#qq.com(#换@),我们将第一时间删除本站数据。

如有侵犯您的版权,请及时联系3500663466#qq.com(#换@),我们将第一时间删除本站数据。

THE END

暂无评论内容