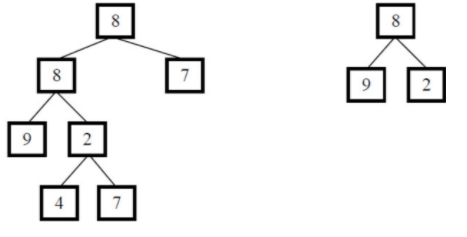

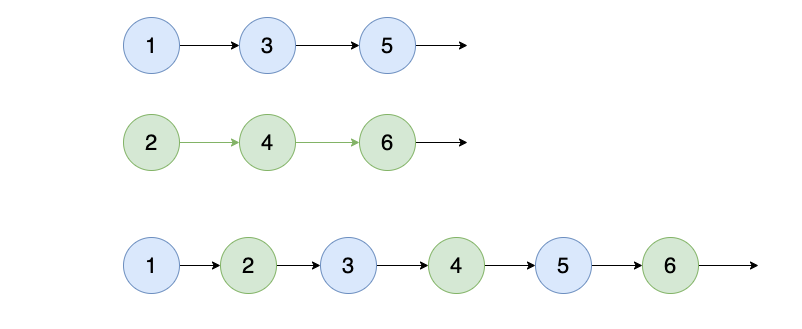

首先查看一下两者的定义:

1,时钟不确定性(Clock Uncertainty):是指在给定时间点上,某个时钟信号可能存在的不确定性范围。它通常是由于信号传播延迟、设备响应时间、时钟抖动等导致的。这种不确定性关注的是在做出时间测量时,设备时间值的准确性和可靠性。uncertainty = jitter+ skew。

2,时钟偏移(Clock Skew):做完CTS后,不同clock tree之间的latency差值。

clock uncertainty的数值来源:

foundry厂会给一个值,一般很保守。

推荐的经验设定值:DC 的时候设置10%, P&R的时候设置5%, PT 的时候设置3%。

两者之间存在一定的联系,uncertainty是模拟的时钟不确定性,clock skew是在CTS确定后的时钟之间的偏差。CTS的skew基于前面place阶段的uncertainty产生。

那么place和CTS阶段的时序差异就表现在这个地方,如果在place阶段的uncertainty比在CTS阶段做出来的的skew更大,那么在CTS之后的timing会更好,如果uncertainty不能cover Skew,那么CTS之后的timing会差一些。

除此之外,place和CTS之间的RC correlation也会影响到这两个阶段的timing。

现在ICC2会全阶段默认开启CCD使用useful skew,那么在place不开,CTS开的情况下,CTS阶段的timing会比place阶段好一些。

—-分割线

常见的问题:为什么CTS后的timing会变差?

1. 可能没有使用Early clock flow,ICG的时序在place阶段分析是过于乐观的,另外place阶段没有考虑时钟的ndr,所以congestion和绕线的影响评估都过于乐观,自然也影响了timing的结果。还有就是uncertainty的设置,如果无法cover skew,那么自然评估就是偏乐观的。还有就是cts阶段会修Hold,它也会让density/util/congestion增高,也会对timing有一部分影响。

2. 要看RC correlation和uncertainty的设置了,如果都是合理的话,那么是可能变好的,因为uncertainty是最差的值,而flop之间的skew是都在uncertainty内的,所以会比它小,所以TNS会变好。另外useful skew也会对timing有利。

TRANSLATE with

x

English

| Arabic | Hebrew | Polish |

| Bulgarian | Hindi | Portuguese |

| Catalan | Hmong Daw | Romanian |

| Chinese Simplified | Hungarian | Russian |

| Chinese Traditional | Indonesian | Slovak |

| Czech | Italian | Slovenian |

| Danish | Japanese | Spanish |

| Dutch | Klingon | Swedish |

| English | Korean | Thai |

| Estonian | Latvian | Turkish |

| Finnish | Lithuanian | Ukrainian |

| French | Malay | Urdu |

| German | Maltese | Vietnamese |

| Greek | Norwegian | Welsh |

| Haitian Creole | Persian |

TRANSLATE with

COPY THE URL BELOW

Back

EMBED THE SNIPPET BELOW IN YOUR SITE

Enable collaborative features and customize widget: Bing Webmaster Portal

Back

没有回复内容